西门子S7-1500模块6ES7512-1SM03-0AB0

-

≥ 1台¥0.00

西门子S7-1500模块6ES7512-1SM03-0AB0

西门子S7-1500模块6ES7512-1SM03-0AB0

西门子S7-1500模块6ES7512-1SM03-0AB0

SIMATIC DP,CPU 1512SP F-1 PN 针对 ET 200SP, 中央处理器,带 工作存储器 600 KB 用于 程序及 2MB 用于数据, 1 个接口:PROFINET IRT 带 3 接口交换机, 25 ns Bit-Performance, 需要 SIMATIC 存储卡, 需要总线适配器用于 接口 1 和 2

1. 有向连线

在顺序功能图中,随着时间的推移和转换条件的实现,将会发生步的活动状态的进展,这种进展按有向连线规定的路线和方向进行。在画顺序功能图时,将代表各步的方框按它们成为活动步的先后次序顺序排列,并且用有向连线将它们连接起来。步的活动状态习惯的进展方向是从上到下或从左至右,在这两个方向有向连线上的箭头可以省略。如果不是上述的方向,应在有向连线上用箭头注明进展方向。在可以省略箭头的有向连线上,为了更易于理解也可以加箭头。

2. 转换

转换用有向连线上与有向连线垂直的短划线来表示,转换将相邻两步分隔开。步的活动状态的进展是由转换的实现来完成的,并与控制过程的发展相对应。

3. 转换条件

使系统由当前步进入下一步的信号称为转换条件,转换条件可以是外部的输入信号,例如按钮、指令开关、限位开关的接通或断开等也可以是PLC内部产生的信号,例如定时器、计数器常开触点的接通等转换条件还可以是若干个信号的与、或、非逻辑组合。

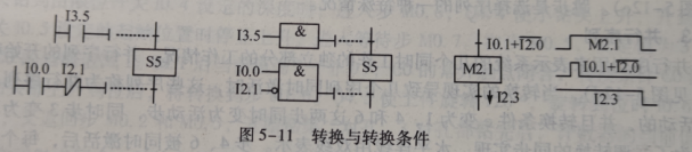

S7-Graph中的转换条件用梯形图或功能块图来表示(见图5-11),如果没有使用S7-Graph语言,一般用布尔代数表达式来表示转换条件。

图5-11的右图用高电平表示步M2.1为活动步,反之则用低电平来表示。转换条件10.0表示10.0为1状态时转换实现,转换条件I0.0表示10.0为0状态时转换实现。转换条件I0.1 12.0表示10.1的常开触点闭合或I2.0的常闭触点闭合时转换实现,在梯形图中则用两个触点的并联来表示这样的“或”逻辑关系。

符号12.3↑和I2.3↓分别表示当I2.3从0状态变为1状态和从1状态变为0状态时转换实现。一般情况下转换条件个I2.3和I2.3是等效的,前级步为活动步时,一旦 I2.3由0 状态变为1状态(即在12.3的上升沿),转换条件I2.3也会马上起作用。

在图5-9中,转换条件T0相当于接通延时定时器T0的常开触点,即在T0的定时时间到时转换条件满足。

| 6ES7211-1BE40-0XB0 | CPU 1211C AC/DC/Rly,6输入/4输出,集成2AI |

| 6ES7211-1AE40-0XB0 | CPU 1211C DC/DC/DC,6输入/4输出,集成2AI |

| 6ES7211-1HE40-0XB0 | CPU 1211C DC/DC/Rly,6输入/4输出,集成2AI |

| 6ES7212-1BE40-0XB0 | CPU 1212C AC/DC/Rly,8输入/6输出,集成2AI |

| 6ES7212-1AE40-0XB0 | CPU 1212C DC/DC/DC,8输入/6输出,集成2AI |

| 6ES7212-1HE40-0XB0 | CPU 1212C DC/DC/Rly,8输入/6输出,集成2AI |

| 6ES7214-1BG40-0XB0 | CPU 1214C AC/DC/Rly,14输入/10输出,集成2AI |

| 6ES7214-1AG40-0XB0 | CPU 1214C DC/DC/DC,14输入/10输出,集成2AI |

| 6ES7214-1HG40-0XB0 | CPU 1214C DC/DC/Rly,14输入/10输出,集成2AI |

| 6ES7215-1BG40-0XB0 | CPU 1215C AC/DC/Rly,14输入/10输出,集成2AI/2AO |

| 6ES7215-1AG40-0XB0 | CPU 1215C DC/DC/DC,14输入/10输出,集成2AI/2AO |

| 6ES7215-1HG40-0XB0 | CPU 1215C DC/DC/Rly,14输入/10输出,集成2AI/2AO |

| 6ES72171AG400XB0 | CPU 1217C DC/DC/DC,14输入/10输出,集成2AI/2AO |