西门子代理触摸屏

-

≥ 1台¥0.00

西门子代理触摸屏

西门子代理触摸屏

西门子代理触摸屏

顺序控制设计法

用经验设计法设计梯形图时,没有一套固定的方法和步骤可以遵循,具有很大的试探性和随意性,对于不同的控制系统,没有一种通用的容易掌握的设计方法。在设计复杂系统的梯形图时,用大量的中间单元来完成记忆,联锁和互领等功能,由于嵩要考虑的因素很多,它们往往又交织在一起,分析起来非常困难,并且很容易遗漏些应该考虑的问题,修改某一局部电路时,很可能会“牵一发而动全身",对系统的其他部分产生意想不到的影响,因此梯形图的修改也很麻烦,往往花了很长的时间还得不到一个消意的结果。用经验法设计出的梯形制往往很难阅读,给系统的维修和改进带来了很大的困难。

所置原序控制,就是按照生产工艺预先规定的顺序,在各个输人信号的作用下,根据内部状态和时间的顺序,在生产过程中各个执行机构自动地有秩序地进行操作。使用顺序控制设计法时根据系统的工艺过程,画出顺序功能图,然后根据顺序功能图画出梯形图,有的可编程序控制器为用户提供了顺序功能图语言,在编程软件中生成顺序功能图后便完成了编程工作。它是一种的设计方法,很容易被初学者接受,对于有经验的工程师,也会提高设计的效率,程序的调试修改和阅读也很方便。某厂有经验的电气工程师用经验设计法设计某控制系统的梯形图,花了两周的时间,同一系统改用顺序控制设计法,只用了不到半天的时间,就完成了梯形图的设计和模拟调试,现场试车一次成功。

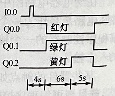

顺序控制设计法基本的思想是将系统的一个工作周期划分为若干个顺序相连的阶段,这些阶段称为步(Step),并用编程元件(例如位存储器M和顺序控制维电器S)来代表各步。步是根据输出量的状态变化来划分的,在任何一步之内,各输出量的0N/OFF状态不变,但是相邻两步输出量的状态是不同的(见图411)。步的这种划分方法使代表各步的编程元件的状态与各输出量的状态之间有着极为简单的逻辑关系。

图411步的划分

使系统由当前步进人下一步的信号称为转换条件,转换条件可以是外部的输人信号,如按钮、指令开关、限位开关的技迎/断开等;也可以是可编程序拉生器内部产生的信母,如定时器、计数器常开触点的接通等。转换条件还可能是若干个信号的与、或、非逻辑组合。

顺序控制设计法用转换条件控制代表各步的编程元件,让它们的状态按一定的顺序变化,然后用代表各步的编程元件去控制可编程序控制器的各输出位。

顺序功能图的由来

顺序功能图(Sequential Function Charl)是描述控制系统的控制过程、功能和特性的一种图形,也是设计可编程序控制器的顺序控制程序的有力工具。

顺序功能图并不涉及所描述的控制功能的具体技术,它是一种通用的技术语言,可以供进一步设计和不同的人员之间进行技术交流之用。

在法国的TE(Telemecanique)公司研制的Grafcel的基础上,1978年法国公布了用于工业过程文件编制的法国标准Afcet,第二年公布了功能图(Funetin Chart)的国家标准Grafcet,它提供了所谓的步(Step)和转换(Transition)这两种简单的结构,这样可以将系统划分为简单的单元,并定义出这些单元之问的顺序关系。

1994年5月公布的IFC可编程序控制器标准(IEC1131)中,顺序功能图被确定为可编程序控制器的编程语言。我国也在1986年颁布了顺序功能图的国家标准GB6988.6-1986。顺序功能图主要由步、有向连线、转换、转换条件和动作(或命令)组成。

何为PLC的周期扫描机制?PLC的扫描周期一般包括哪几个阶段?

当PLC运行时,CPU就要执行用户程序中的操作。但是CPU不可能同时执行多个操作,只能分时地一个操作一个操作地执行。PLC利用系统软件在其内部建立了输入输出映像区,当PLC的CPU执行用户程序时,从输入映像区中读取输入信号的状态,进行相应的操作。当CPU执行完个操作后,将操作结果输出到输出映像区,然后再执行第二个操作,操作结果送到输出映像区。在程序执行过程中,PLC并不读取输入信号的真正状态,执行结果也并没有输出到PLC外部。只有当程序执行到结束指令(END)时,将输出映像区中执行结果向PLC外部输出一次,将输入信号的状态读取一次送到输入映像区。对输入输出信号的这一操作过程称为I/O刷新。I/O刷新完成后,CPU再从用户程序的条指令开始,进行下一次程序执行。PLC的这种工作方式被称为扫描方式。

PLC的扫描周期包括上电后初始处理、共同处理、上位链接服务、外设服务、运算处理、I/O刷新。

| 6ES7211-1BE40-0XB0 | CPU 1211C AC/DC/Rly,6输入/4输出,集成2AI |

| 6ES7211-1AE40-0XB0 | CPU 1211C DC/DC/DC,6输入/4输出,集成2AI |

| 6ES7211-1HE40-0XB0 | CPU 1211C DC/DC/Rly,6输入/4输出,集成2AI |

| 6ES7212-1BE40-0XB0 | CPU 1212C AC/DC/Rly,8输入/6输出,集成2AI |

| 6ES7212-1AE40-0XB0 | CPU 1212C DC/DC/DC,8输入/6输出,集成2AI |

| 6ES7212-1HE40-0XB0 | CPU 1212C DC/DC/Rly,8输入/6输出,集成2AI |

| 6ES7214-1BG40-0XB0 | CPU 1214C AC/DC/Rly,14输入/10输出,集成2AI |

| 6ES7214-1AG40-0XB0 | CPU 1214C DC/DC/DC,14输入/10输出,集成2AI |

| 6ES7214-1HG40-0XB0 | CPU 1214C DC/DC/Rly,14输入/10输出,集成2AI |

| 6ES7215-1BG40-0XB0 | CPU 1215C AC/DC/Rly,14输入/10输出,集成2AI/2AO |

| 6ES7215-1AG40-0XB0 | CPU 1215C DC/DC/DC,14输入/10输出,集成2AI/2AO |

| 6ES7215-1HG40-0XB0 | CPU 1215C DC/DC/Rly,14输入/10输出,集成2AI/2AO |

| 6ES72171AG400XB0 | CPU 1217C DC/DC/DC,14输入/10输出,集成2AI/2AO |