软硬结合板HDI加工,刚柔结合板

-

面议

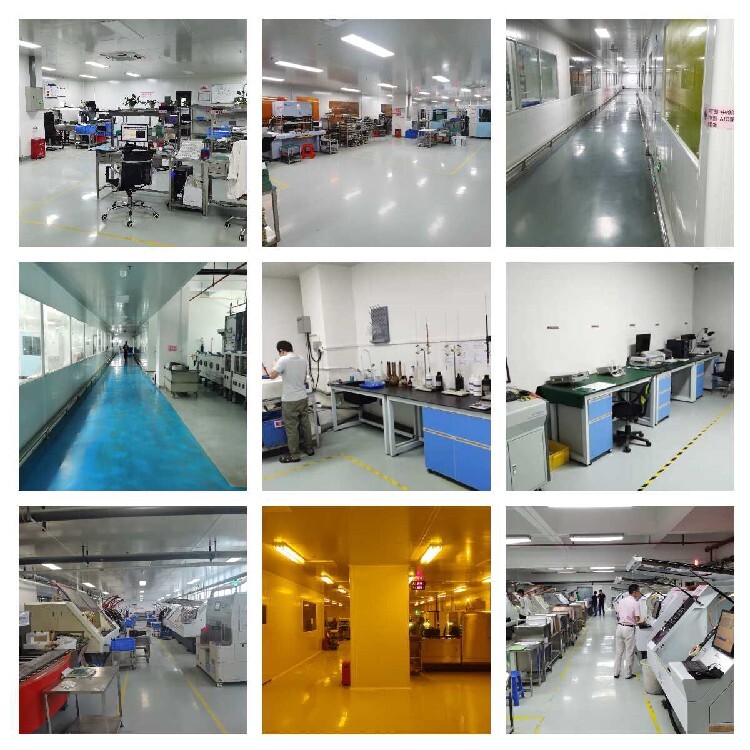

深圳市赛孚电路科技有限公司成立于2011年,公司由多名电路板行业的级人士创建,是国内的PCB/FPC快件服务商之一。公司成立以来,一直专注样品,中小批量领域。快速的交付以及过硬的产品品质赢得了国内外客户的信任。公司是广东电路板行业协会会员企业,是深圳高新技术认证企业。拥有完善的质量管理体系,先后通过了ISO9001、ISO14000、TS16949、UL、RoHS认证。公司目前拥有员工300余人,厂房面积9000平米,月出货品种6000种以上,年生产能力为150000平方米。为了满足客户多样化需求,2017年公司成立了PCBA事业部,自有SMT生产线,为客户提供PCB+SMT一站式服务。 公司一直致力于“打造中国的PCB制造企业”。注重人才培养,倡导全员“自我经营”理念,拥有一支朝气蓬勃、敬业、经验丰富的技术、生产及管理队伍;专注于PCB的工艺技术的研究与开发,努力提升公司在PCB领域内的技术水平和制造能力.

公司产品广泛应用于通信、工业控制、计算机应用、航空航天、、医疗、测试仪器、电源等各个领域。我们的产品包括:高多层PCB、HDI PCB、PCB高频板、软硬结合板、FPC等特种高难度电路板,专注于多品种,中小批量领域。我们的客户分布各地,目前外销订单占比70%以上。

赛孚电路秉承“以人为本,客户至上”的企业经营理念,“以质量为根,服务为本 ” 的企业服务宗旨,坚持持之以恒的精神,全员参与质量改进,不断吸纳国际新技术,完善产品品质,积极吸引和培养管理及技术人才,以确保向客户提供更好的服务,为客户创造更多价值,与客户共同成长。

高精密度(HDI板)电路板的耐热性介绍

HDI板的耐热性能是HDI可靠性能中重要的一个项目,HDI板的板厚变得越来越薄,对其耐热性能的要求也越来越高。无铅化进程的推进,也提高了HDI板耐热性能的要求,而且由于HDI板在层结构等方面不同于普通多层通孔PCB板,因此HDI板的耐热性能与普通多层通孔PCB板相比有所不同,一阶HDI板典型结构。HDI板的耐热性能缺陷主要是爆板和分层。到目前为止,根据多种材料以及多款HDI板的耐热性能测试的经验,发现HDI板发生爆板机率大的区域是密集埋孔的上方以及大铜面的下方区域。

耐热性是指PCB抵抗在焊接过程中产生的热机械应力的能力, PCB在耐热性能测试中发生分层的机制一般包括以下几种:

1) 测试样品内部不同材料在温度变化时,膨胀和收缩性能不同而在样品内部产生内部热机械应力,从而导致裂缝和分层的产生。

2) 测试样品内部的微小缺陷(包括空洞,微裂纹等),是热机械应力集中所在,起到应力的放大器的作用。在样品内部应力的作用下,更加容易导致裂缝或分层的产生。

3) 测试样品中挥发性物质(包括有机挥发成分和水),在高温和剧烈温度变化时,急剧膨胀产生的内部蒸汽压力,当膨胀的蒸汽压力到达测试样品内部的微小缺陷(包括空洞,微裂纹等)时,微小缺陷对应的放大器作用就会导致分层。

HDI板容易在密集埋孔的上方发生分层,这是由于HDI板在埋孔分布区域特殊的结构所导致的。有无埋孔区域的应力分析如下表1。无埋孔区域(结构1)在耐热性能测试受热膨胀时,在同一平面上各个位置的Z方向的膨胀量都是均匀的,因此不会存在由于结构的差异造成的应力集中区域。当区域中设计有埋孔且埋孔钻在基材面上(结构2)时,在埋孔与埋孔之间的A-A截面上,由于基材没有收到埋孔在Z方向的约束,因而膨胀量较大,而在埋孔和焊盘所在的B-B截面上,由于基材受到埋孔在Z方向的约束,因而膨胀量较小,这三处膨胀量的差异,在埋孔焊盘与HDI介质和塞孔树脂交界处和附近区域造成应力集中,从而比较容易形成裂缝和分层。

HDI板容易在外层大铜面的下方发生分层,这是由于在贴装和焊接时,PCB受热,挥发性物质(包括有机挥发成分和水)急剧膨胀,外层大铜面阻挡了挥发性物质(包括有机挥发成分和水)的及时逸出,因此产生的内部蒸汽压力,当膨胀的蒸汽压力到达测试样品内部的微小缺陷(包括空洞,微裂纹等)时,微小缺陷对应的放大器作用就会导致分层。

超实用的高频PCB电路设计70问答 之二

21.在电路板尺寸固定的情况下,如果设计中需要容纳更多的功能,就往往需要提高 PCB 的走线密度,但是这样有可能导致走线的相互干扰增强,同时走线过细也使阻抗无法降低,请介绍在高速(>100MHz)高密度 PCB 设计中的技巧?

在设计高速高密度 PCB 时,串扰(crosstalk interference)确实是要特别注意的,因为它对时序(timing)与信号完整性(signal integrity)有很大的影响。以下提供几个注意的地方:

控制走线特性阻抗的连续与匹配。

走线间距的大小。一般常看到的间距为两倍线宽。可以透过仿真来知道走线间距对时序及信号完整性的影响,找出可容忍的小间距。不同芯片信号的结果可能不同。

选择适当的端接方式。

避免上下相邻两层的走线方向相同,甚至有走线正好上下重叠在一起,因为这种串扰比同层相邻走线的情形还大。

利用盲埋孔(blind/buried via)来增加走线面积。但是 PCB 板的制作成本会增加。在实际执行时确实很难达到完全平行与等长,不过还是要尽量做到。

除此以外,可以预留差分端接和共模端接,以缓和对时序与信号完整性的影响。

22.电路板 DEBUG 应从那几个方面着手?

就数字电路而言,先依序确定三件事情: 1. 确认所有电源值的大小均达到设计所需。有些多重电源的系统可能会要求某些电源之间起来的顺序与快慢有某种规范。 2. 确认所有时钟信号频率都工作正常且信号边缘上没有非单调(non-monotonic)的问题。3. 确认 reset 信号是否达到规范要求。 这些都正常的话,芯片应该要发出个周期(cycle)的信号。接下来依照系统运作原理与 bus protocol 来 debug。

23、滤波时选用电感,电容值的方法是什么?

电感值的选用除了考虑所想滤掉的噪声频率外,还要考虑瞬时电流的反应能力。如 果 LC 的输出端会有机会需要瞬间输出大电流,则电感值太大会阻碍此大电流流经此电感的速度,增加纹波噪声(ripple noise)。电容值则和所能容忍的纹波噪声规范值的大小有关。纹波噪声值要求越小,电容值会较大。而电容的ESR/ESL 也会有影响。另外,如果这 LC 是放在开关式电源(switching regulation power)的输出端时,还要注意此 LC 所产生的极点零点(pole/zero)对负反馈控制(negative feedback control)回路稳定度的影响。

24、模拟电源处的滤波经常是用 LC 电路。但是为什么有时 LC 比 RC 滤波效果差?

LC与 RC滤波效果的比较考虑所要滤掉的频带与电感值的选择是否恰当。因为电感的感抗(reactance)大小与电感值和频率有关。如果电源的噪声频率较低,而电感值又不够大,这时滤波效果可能不如 RC。但是,使用 RC 滤波要付出的代价是电阻本身会耗能,效率较差,且要注意所选电阻能承受的功率。

25、如何尽可能的达到 EMC 要求,又不致造成太大的成本压力?

PCB 板上会因 EMC 而增加的成本通常是因增加地层数目以增强屏蔽效应及增加了 ferrite bead、choke等抑制高频谐波器件的缘故。除此之外,通常还是需搭配其它机构上的屏蔽结构才能使整个系统通过 EMC的要求。以下仅就 PCB 板的设计技巧提供几个降低电路产生的电磁辐射效应。

尽可能选用信号斜率(slew rate)较慢的器件,以降低信号所产生的高频成分。

注意高频器件摆放的位置,不要太靠近对外的连接器。

注意高速信号的阻抗匹配,走线层及其回流电流路径(return current path), 以减少高频的反射与辐射。

在各器件的电源管脚放置足够与适当的去耦合电容以缓和电源层和地层上的噪声。特别注意电容的频率响应与温度的特性是否符合设计所需。

对外的连接器附近的地可与地层做适当分割,并将连接器的地就近接到 chassis ground。

可适当运用 ground guard/shunt traces 在一些特别高速的信号旁。但要注意 guard/shunt traces 对走线特性阻抗的影响。

电源层比地层内缩 20H,H 为电源层与地层之间的距离。