连云港出售碳化硅肖特基二极管联系方式

-

面议

SiC PiN 的击穿电压很高,开关速度很快,重量很轻,并且体积很小,它在 3KV以上的整流器应用领域更加具有优势。2000年Cree公司研制出19.5 KV的台面PiN二极管,同一时期日本的 Sugawara 研究室也研究出了 12 KV 的台面 PiN 二极管。2005 年 Cree 公司报道了 10 KV、3.75 V、50 A 的 SiC PiN 二极管,其 10 KV/20 A PiN二极管系列的合格率已经达到 40%。

SBD 在导通过程中没有额外载流子的注入和储存,因而反向恢复电流小,关断过程很快,开关损耗小。传统的硅肖特基二极管,由于所有金属与硅的功函数差都不很大,硅的肖特基势垒较低,硅 SBD 的反向漏电流偏大,阻断电压较低,只能用于一二百伏的低电压场合且不适合在 150 ℃以上工作。然而,碳化硅 SBD弥补了硅 SBD 的不足,许多金属,例如镍、金、钯、钛、钴等,都可以与碳化硅形成肖特基势垒高度 1 eV 以上的肖特基接触。据报道,Au/4H-SiC 接触的势垒高度可达到 1.73 eV,Ti/4H-SiC 接触的势垒比较低,但高也可以达到 1.1 eV。6H-SiC与各种金属接触之间的肖特基势垒高度变化比较宽,低只有 0.5 eV,高可达1.7 eV。于是,SBD 成为人们开发碳化硅电力电子器件关注的对象。它是高压快速与低功率损耗、耐高温相结合的理想器件。目前国际上相继研制成功水平较高的多种类的碳化硅器件。

国内的SiC功率器件研究方面因为受到 SiC 单晶材料和外延设备的限制起步比较晚,但是却紧紧跟踪国外碳化硅器件的发展形势。国家十分重视碳化硅材料及其器件的研究, 在国家的大力支持下经已经初步形成了研究 SiC 晶体生长、SiC器件设计和制造的队伍。电子科技大学致力于器件结构设计方面,在新结构、器件结终端和器件击穿机理方面做了很多的工作,并且提出宽禁带半导体器件优值理论和宽禁带半导体功率双极型晶体管特性理论。

功率二极管是功率半导体器件的重要组成部分,主要包括 PiN 二极管,肖特基势垒二极管和结势垒控制肖特基二极管。本章主要介绍了肖特基势垒的形成及其主要电流输运机理。并详细介绍了肖特基二极管和结势垒控制肖特基二极管的电学特性及其工作原理,为后两章对 4H-SiC JBS 器件电学特性的仿真研究奠定了理论基础。

金属与 N 型 4H-SiC 半导体体内含有大量的导电载流子。金属与 4H-SiC 半导体材料的接触仅有原子大小的数量级间距时,4H-SiC 半导体的费米能级大于金属的费米能级。此时 N 型 4H-SiC 半导体内部的电子浓度大于金属内部的电子浓度,两者接触后,导电载流子会从 N 型 4H-SiC 半导体迁移到金属内部,从而使 4H-SiC 带正电荷,而金属带负电荷。电子从 4H-SiC 向金属迁移,在金属与 4H-SiC 半导体的界面处形成空间电荷区和自建电场,并且耗尽区只落在 N 型 4H-SiC 半导体一侧,在此范围内的电阻较大,一般称作“阻挡层”。自建电场方向由 N 型 4H-SiC 内部指向金属,因为热电子发射引起的自建场增大,导致载流子的扩散运动与反向的漂移运动达到一个静态平衡,在金属与4H-SiC 交界面处形成一个表面势垒,称作肖特基势垒。4H-SiC 肖特基二极管就是依据这种原理制成的。

产生二次击穿的原因主要是半导体材料的晶格缺陷和管内结面不均匀等引起的。二次击穿的产生过程是:半导体结面上一些薄弱点电流密度的增加,导致这些薄弱点上的温度增加引起这些薄弱点上的电流密度越来越大,温度也越来越高,如此恶性循环引起过热点半导体材料的晶体熔化。此时在两电极之间形成较低阻的电流通道,电流密度骤增,导致肖特基二极管还未达到击穿电压值就已经损坏。因此二次击穿是不可逆的,是破坏性的。流经二极管的平均电流并未达到二次击穿的击穿电压值,但是功率二极管还是会产生二次击穿。

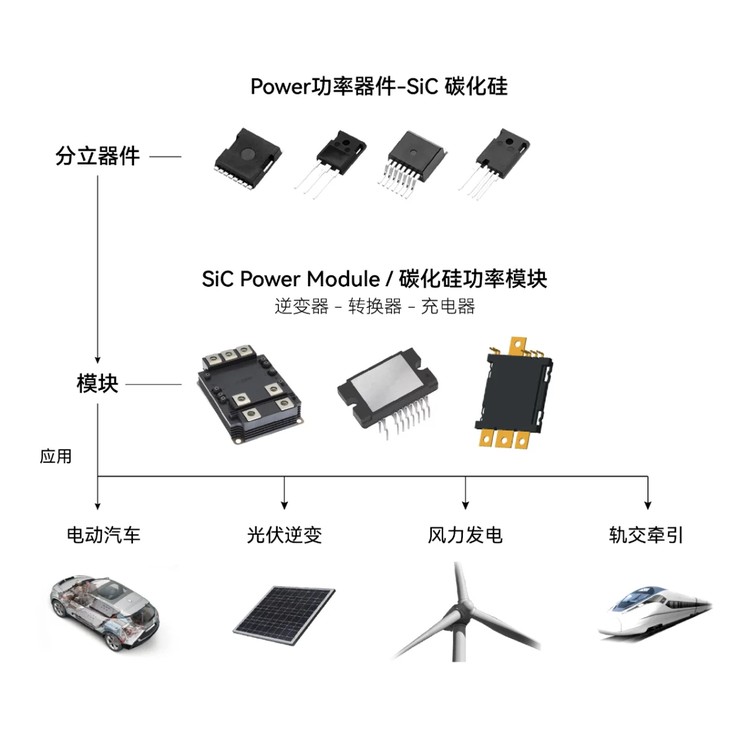

碳化硅作为一种宽禁带半导体材料,比传统的硅基器件具有更的性能。碳化硅的宽禁带(3.26eV)、高临界场(3×106V/cm)和高导热系数(49W/mK)使功率半导体器件效率更高,运行速度更快,能够有效降低产品成本、体积及重量。

碳化硅具有载流子饱和速度高和热导率大的特点,应用开关频率可达到1MHz,在高频应用中优势明显,其中碳化硅肖特基二极管(SiC JBS)耐压可以达到6000V以上。相对应的,硅材料的禁带宽度较低,在较低的温度下硅器件本征载流子浓度较高,而高的漏电流会造成热击穿,这限制了器件在高温环境和大功率耗散条件下工作。

碳化硅的能带间隔为硅的2.8倍(宽禁带),达到3.09电子伏特。其绝缘击穿场强为硅的5.3倍,高达3.2MV/cm,其导热率是硅的3.3倍,为49w/cm·k。它与硅半导体材料一样,可以制成结型器件、场效应器件、和金属与半导体接触的肖特基二极管。